### NORTHWESTERN UNIVERSITY

# High Performance and Energy Efficient Computer System Design Using Photonic Interconnects

#### A DISSERTATION

# SUBMITTED TO THE GRADUATE SCHOOL IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

for the degree

DOCTOR OF PHILOSOPHY

Field of Electrical Engineering and Computer Science

By

YIGIT DEMIR

EVANSTON, ILLINOIS

August 2015

### **Abstract**

Silicon photonics have emerged as a promising solution to meet the growing demand for high-bandwidth, low-latency, and energy-efficient communication in manycore and multi-chip processors. Multi-chip designs can leverage nanophotonic interconnects to realize high performance "virtual chips" with the aggregate area and performance much higher than the single-chip multiprocessors. While much work has been done on the architecture, design, and analysis of optical interconnects, the laser is generally excluded from the analysis, and assumed to be lumped into a static off-chip power overhead that we should not be concerned much about. Unfortunately, the wall-plug laser consumption constitutes a major component of the overall power consumption of an optical interconnect. Another major contributor of the optical interconnect's power consumption is the ring-heating power. Photonic interconnects are primarily based on microrings, which are highly sensitive to temperature. As a result, current silicon-photonic interconnect designs expend a significant amount of energy heating the microrings to a designated narrow temperature range, only to have the majority of the thermal energy waste away and dissipate through the heat sink, and in the process of doing so heat up the logic layer, causing significant performance degradation to the cores and inducing thermal emergencies. As a result, the laser power and the ring heating power consumption remains a potential issue that needs to be addressed.

The scalability trends of modern semiconductor technology lead to increasingly dense multicore chips. Unfortunately, physical limitations in area, power, off-chip bandwidth, and yield constrain single-chip designs to a relatively small number of cores, beyond which scaling becomes impractical. Multi-chip designs overcome these constraints, and can reach scales impossible to realize with conventional single-chip architectures. However, to deliver commensurate performance, multi-chip architectures require a cross-chip interconnect with bandwidth, latency, and energy consumption well beyond the reach of electrical signaling. We propose Galaxy, an architecture that enables the construction of a many-core "virtual chip" by connecting multiple smaller chiplets through optical fibers. The low optical loss of fibers allows the flexible placement of chiplets, and offers simpler packaging, power, and heat requirements. At the same time, the low latency and high bandwidth density of optical signaling maintain the tight coupling of cores, allowing the virtual chip to match the performance of a single chip that is not subject to area, power, and bandwidth limitations. Our results indicate that Galaxy is up to 3.4x faster (1.8-2.2x on average) over single-chip alternatives and achieves up to 6.8x smaller energy-delay product (2.6x on average), and scales to 4K cores while being 2.5x faster at 6x lower laser power than a waveguide-based design.

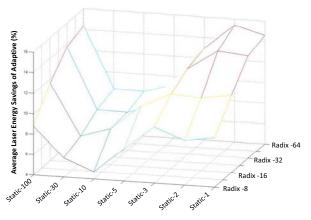

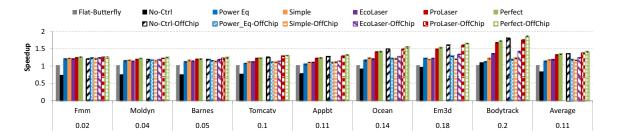

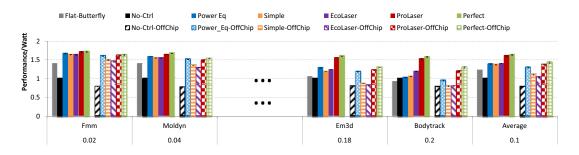

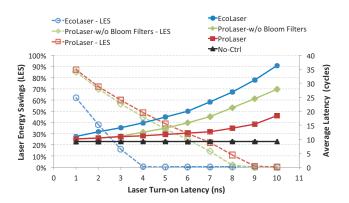

Photonic interconnects provide low cost signal modulation, and low latency communication, however, high optical loss of many nanophotonic components results in high power requirements for the laser source and thermal sensitivity of photonic devices force designers to have power hungry chip level ring-heating solutions. In this work, we propose EcoLaser, an adaptive laser control mechanism that saves laser power by turning the laser off when not needed, while at the same time meeting high bandwidth requirements by leaving the laser on longer. Our results indicate that EcoLaser saves up to 77% laser energy. Furthermore, we propose ProLaser, which is a laser control scheme that improves the EcoLaser scheme by keeping the majority of the data-bus inactive while sending small (dataless) messages, and anticipating upcoming messages to turn the

lasers on ahead of time. Our results indicate that ProLaser achieves even higher energy savings (up to 88%). On top of that, the power savings of ProLaser allow for providing a higher power budget to the cores, which enables them to run faster. Employing ProLaser on a topology with SWMR crossbars (Firefly [57]) allows the multicore to achieve 1.5-1.7x speedup (1.6x on average) and attain 35-52% lower energy consumption per instruction (40% on average).

Our results show that laser control is a powerful technique that improves the energy-efficiency of the photonic interconnects, so we extend our laser control techniques to Flattened Butterfly which is a scalable topology. We propose SLAC, a laser control scheme for flattened butterfly network which turns off majority of the network to save laser energy, while maintaining a fully connected network, which removes the laser turn-on latency from the critical path and causes minimal (next to nothing) performance decrease. SLAC turns off majority of the network when the utilization is low to save energy and activates additional stages when the utilization is high to provide better performance. From an on-chip interconnect to a datacenter network, any network with flattened butterfly topology can take advantage of SLAC. Our results show that, for on-chip and multichip applications, SLAC can save up to 67% laser energy while reducing the performance by only 2% while running real-world workloads. On a flattened butterfly datacenter network, SLAC saves 79% laser energy on average while running traces collected from university servers.

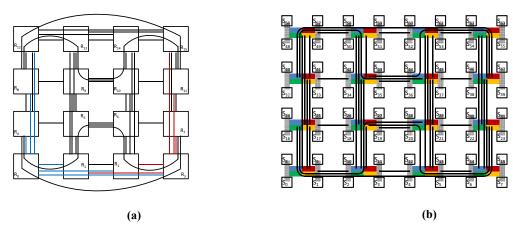

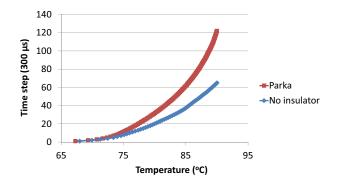

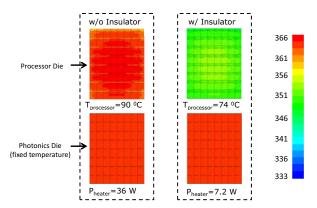

The nanophotonic devices are highly susceptible to temperature-induced changes, because their refraction index changes rapidly with temperature. In a multicore processor there is a potential for significant variation in temperature, so micro-ring resonators must be stabilized at a higher temperature using ring heaters which may consume significant amount of energy. We propose "Parka", a nanophotonic NoC that encases the photonic die in a thermal insulator that keeps its

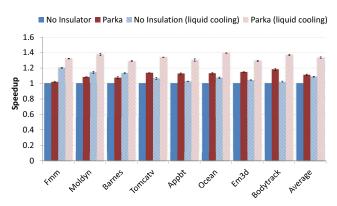

temperature stable with low energy expenditure, while minimizing the spatial and temporal thermal coupling between logic and silicon-photonic components. Our results indicate that Parka reduces the ring heating power by 3.8x on average across our workload suite. Moreover, the energy savings allow for providing a higher power budget to the cores, which enables them to run faster. Parka on a radix-16 crossbar allows the multicore to achieve 11-23% speedup (34% max) over a baseline scheme with no insulation, depending on the cooling solution used. All of the schemes we propose make the photonic interconnects, as well as the multicore processors more energy efficient, which makes the photonic interconnects a more attractive and feasible solution.

### Acknowledgements

First of all, I would like to express my gratitude to my advisor Prof. Nikos Hardavellas. Thank you for teaching me how to do research, constantly encouraging me to think differently, challenging my ideas, and working with me side-by-side for countless hours. This work wouldn't existed without your guidance and help.

Special thanks to Prof. Gokhan Memik, Prof. John Kim and Prof. Russ Joseph for making time to serve in my thesis committee and review this work. Thank you for sharing your knowledge and insight, your comments and help have made this work successful.

I would like to thank my collaborators Pan Yan and Seukwoo Song.

I was very lucky to have George and Ali Murat as my labmates, so thank you guys for sharing your thoughts, ideas, food and drinks with me. I am thankful to my roommate Besim for being there for me whenever I needed help, and cooking all those tasty late night snacks.

Lastly, I would like to thank my family Yasemin, Mustafa, Tuna and my girlfriend for their unconditional love and support.

## **Table of Contents**

| Abstract     | •••••   | •••••••••••••••••••••••••••••••••••••••     | 2  |

|--------------|---------|---------------------------------------------|----|

| Acknowled    | gements | s                                           | 6  |

| List of Figu | ires    |                                             | 10 |

| List of Tab  | les     |                                             | 14 |

| Chapter 1    | Intro   | duction                                     | 18 |

| Chapter 2    | Energ   | gy-Efficient Disintegrated Processor Design | 23 |

| 2.1          | .The C  | Galaxy Architecture                         | 28 |

|              | 2.1.1   | Network Topology                            | 28 |

|              | 2.1.2   | Switch Arbitration and Flow Control         | 31 |

|              | 2.1.3   | Inter-Chiplet Optical Connection            | 32 |

|              | 2.1.4   | Nanophotonic Parameters and Power Budget    | 33 |

| 2.2          | .Expei  | rimental Methodology                        | 35 |

|              | 2.2.1   | Power and Temperature Modeling              | 37 |

|              | 2.2.2   | Resonant Ring Heater Modeling               | 38 |

|              | 2.2.3   | Modeling Memory and Physical Constrains     | 38 |

|              | 2.2.4   | Modeling Large-Scale Designs                | 38 |

| 2.3          | .Expe   | rimental Results                            | 40 |

|           | 2.3.1       | Network Performance                                      | 40           |

|-----------|-------------|----------------------------------------------------------|--------------|

|           | 2.3.2       | Comparison to Single-Chip Designs                        | 40           |

|           | 2.3.3       | Comparison to Multi-Chip Designs                         | 44           |

|           | 2.3.4       | Thermal Evaluation                                       | 47           |

| 2.4       | Limita      | ations and Challenges                                    | 48           |

|           | 2.4.1       | Misalignment and Fiber Density Considerations            | 48           |

|           | 2.4.2       | Board-Level Effects                                      | 50           |

|           | 2.4.3       | Yield, Cost and Lifetime Considerations                  | 50           |

|           |             |                                                          |              |

| Chapter 3 | Intro<br>55 | ducing Laser Control for Energy Proportional Photonic In | nterconnects |

| 3.1       | Backg       | ground                                                   | 58           |

| 3.2       | Nanop       | photonic Interconnect Topologies                         | 61           |

| 3.3       | EcoLa       | aser's Laser Control Schemes                             | 62           |

|           | 3.3.1       | Laser Control for SWMR Crossbar                          | 62           |

|           | 3.3.2       | Laser Control for MWSR Crossbar                          | 63           |

|           | 3.3.3       | Adaptive Laser Control                                   | 67           |

|           | 3.3.4       | The Perfect Laser Control.                               | 68           |

| 3.4       | ProLa       | ser's Laser Control Schemes                              | 68           |

|           | 3.4.1       | Segregating the Data from the Control Bits               | 69           |

|           | 3.4.2       | Proactive Laser Turn-On Mechanism                        | 70           |

| 3.5       | Exper | imental Methodology                                   | 73 |

|-----------|-------|-------------------------------------------------------|----|

|           | 3.5.1 | Interconnect Performance and Energy Analysis          | 73 |

|           | 3.5.2 | Multicore System Performance and Energy Analysis      | 74 |

|           | 3.5.3 | Laser Power Consumption Calculation                   | 77 |

|           | 3.5.4 | Sensitivity to Optical Parameters                     | 77 |

|           | 3.5.5 | Resonant Ring Heater Modeling                         | 78 |

| 3.6       | Exper | imental Results for EcoLaser                          | 78 |

|           | 3.6.1 | Network Performance                                   | 78 |

|           | 3.6.2 | Performance cost of Laser Control                     | 80 |

|           | 3.6.3 | Impact of EcoLaser on a Realistic Multicore           | 82 |

| 3.7       | Exper | imental Results for ProLaser                          | 83 |

|           | 3.7.1 | Network Performance                                   | 83 |

|           | 3.7.2 | Performance cost of Laser Control                     | 85 |

|           | 3.7.3 | Impact of EcoLaser on a Realistic Multicore           | 87 |

|           | 3.7.4 | Case Study: Radix-16 SWMR                             | 88 |

|           | 3.7.5 | Case Study: Firefly                                   | 90 |

|           | 3.7.6 | Laser Turn-on Latency Tolerance                       | 92 |

| Chapter 4 | Intro | ducing Laser Control in a Flattened Butterfly Network | 94 |

| 4.1       | Motiv | ation                                                 | 94 |

|           |       |                                                       |    |

3.4.3

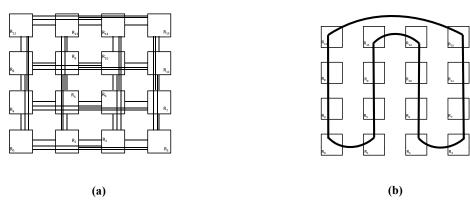

| 4.2       | Diverge | ent Flattened Butterfly Layout                    | 96  |

|-----------|---------|---------------------------------------------------|-----|

|           | 4.2.1   | .Experimental Methodology                         | 98  |

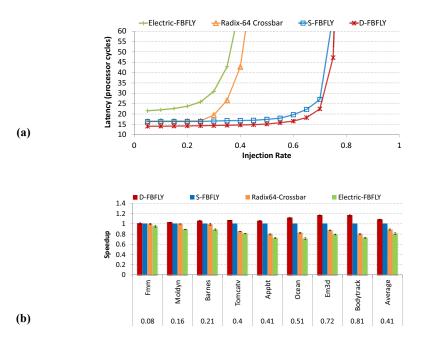

|           | 4.2.2   | .Experimental Results                             | 101 |

| 4.3       | Stage L | Laser Control Scheme                              | 103 |

|           | 4.3.1   | .Experimental Methodology                         | 107 |

|           | 4.3.2   | .Experimental Results                             | 110 |

| Chapter 5 | Systen  | n Level Thermal Tuning Considerations             | 117 |

| 5.1       | Motiva  | ition                                             | 117 |

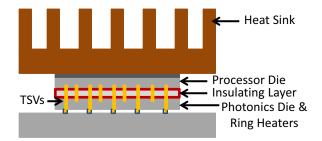

| 5.2       | Photon  | ic Die Insulation with Parka                      | 119 |

| 5.3       | Experi  | mental Methodology                                | 121 |

|           | 5.3.1   | Ring Heater Power Consumption Analysis            | 121 |

|           | 5.3.2   | Multi-core System Performance and Energy Analysis | 122 |

|           | 5.3.3   | Interconnect and Nanophotonic Parameters          | 124 |

|           | 5.3.4   | Modeling Cooling Solutions                        | 125 |

| 5.4       | Experi  | mental Results                                    | 126 |

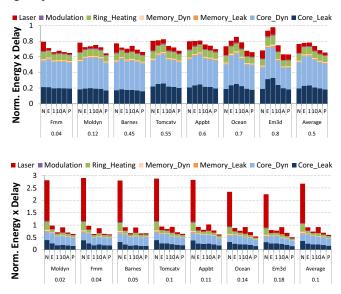

|           | 5.4.1   | Impact on the Ring-Heating Power Consumption      | 126 |

|           | 5.4.2   | Impact on Processor Temperature                   | 130 |

|           | 5.4.3   | Impact on A Realistic Multicore                   | 133 |

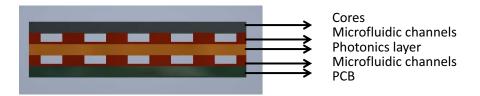

| 5.5       | Photon  | ic Die Insulation with Microfluidic Cooling       | 133 |

|             | 5.5.1  | Evaluation Methodology |      |

|-------------|--------|------------------------|------|

|             | 5.5.2  | Experimental Results   | 135  |

| 5.6         | Limita | tions and Challenges   | 137  |

| Chapter 6   | Discus | ssion and Future Work  | 139  |

|             | Relate | ed Work                | 1341 |

| Chapter 7   | Concl  | lusion                 | 144  |

| Ribliograph | 1V     |                        | 146  |

.

# List of Figures

| Figure     | Title                                                                          | Page         |

|------------|--------------------------------------------------------------------------------|--------------|

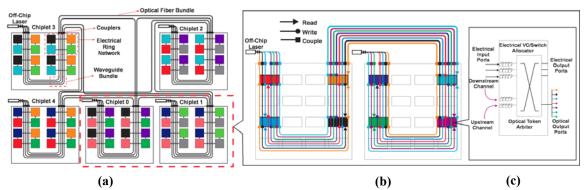

| FIGURE 1:  | (a) Galaxy layout, (b) MWSR optical crossbar, and (c) router architecture      | 29           |

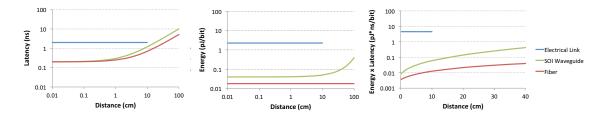

| FIGURE 2:  | Latency, Energy / bit, and Energy x Delay product for electrical links, SOI wa | veguides,    |

|            | and fibers.                                                                    | 32           |

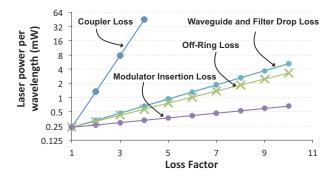

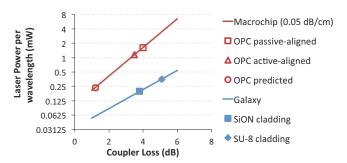

| FIGURE 3:  | Laser power sensitivity to optical parameters.                                 | 35           |

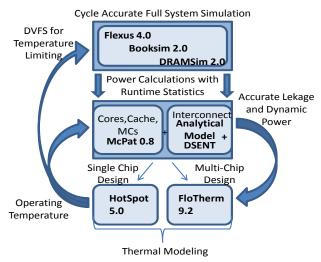

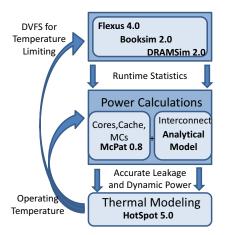

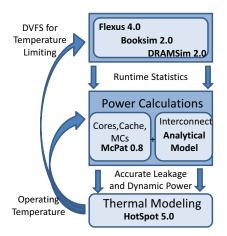

| FIGURE 4:  | Simulation flow chart.                                                         | 37           |

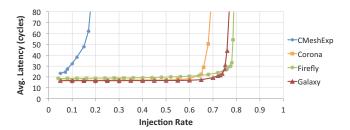

| FIGURE 5:  | Load latency under uniform random traffic.                                     | 40           |

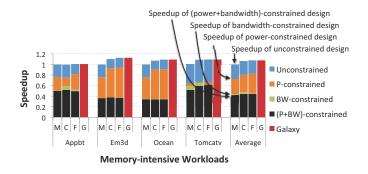

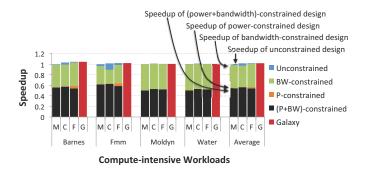

| FIGURE 6:  | Speedup of constrained and unconstrained architectures: CMeshExp (M), Core     | ona (C),     |

|            | Firefly (F), and Galaxy (G).                                                   | 42           |

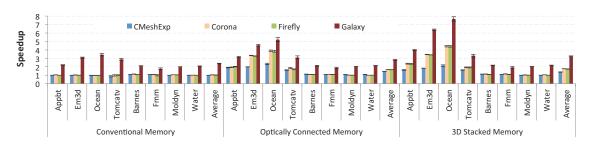

| FIGURE 7:  | Speedup of power-constrained designs with various memory technologies (no      | rmalized to  |

|            | CMeshExp with DDR3).                                                           | 43           |

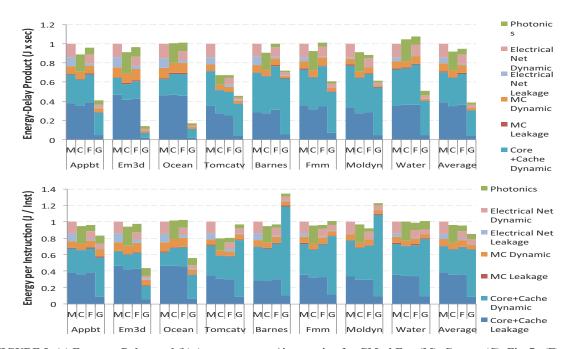

| FIGURE 8:  | (a) Energy x Delay, and (b) Average energy / instruction for CMeshExp (M), (   | Corona (C),  |

|            | Firefly (F), and Galaxy (G).                                                   | 45           |

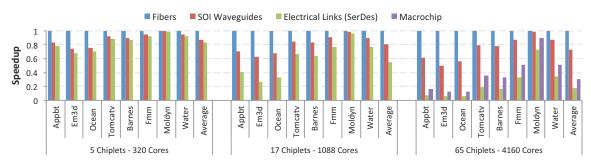

| FIGURE 9:  | Comparison of Galaxy with different chiplet-to-chiplet interconnect technolog  | ies, and the |

|            | Oracle Macrochip.                                                              | 45           |

| FIGURE 10: | Laser power sensitivity to coupler loss.                                       | 47           |

| FIGURE 11: | Thermal effects of chiplet placement.                                          | 47           |

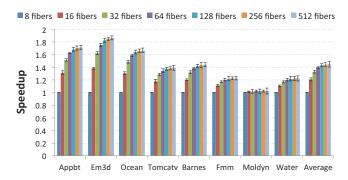

| FIGURE 12: | Sensitivity to fiber density per chiplet                                       | 49           |

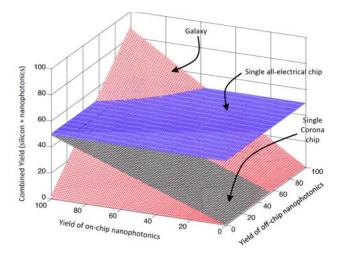

| FIGURE 13: | Impact of panophotonics on overall yield                                       | 51           |

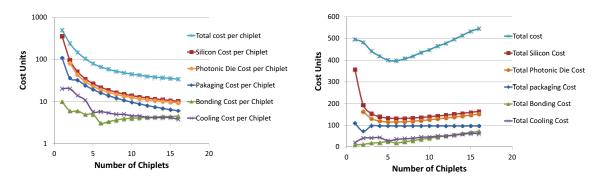

| FIGURE 14: | Impact of disintegration on the cost of each chiplet (right) and the total processor cost |

|------------|-------------------------------------------------------------------------------------------|

|            | (left)                                                                                    |

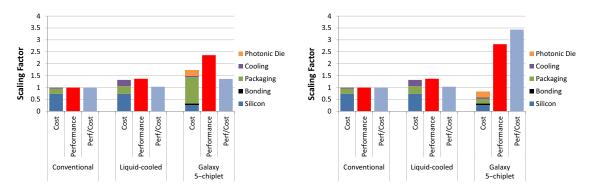

| FIGURE 15: | Cost breakdown for Galaxy with traditional memory connection (left) and optical           |

|            | memory connection (right) compared to Convetional and Liquid-cooled single-chip           |

|            | designs                                                                                   |

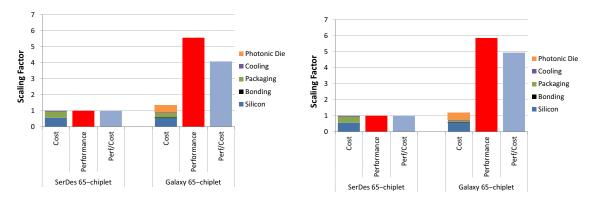

| FIGURE 16: | Cost breakdown for a scaled-out Galaxy with traditional memory connection (left) and      |

|            | optical memory connection (right) compared to a scaled-out design with electrical         |

|            | (SerDes) chip-to-chip cennections54                                                       |

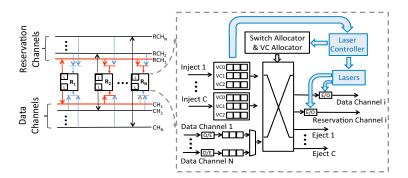

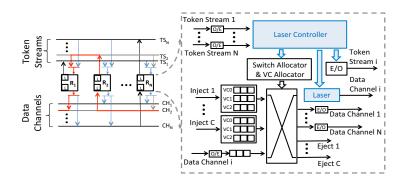

| FIGURE 17: | SWMR crossbar and router microarchitecture                                                |

| FIGURE 18: | MWSR crossbar and router microarchitecture                                                |

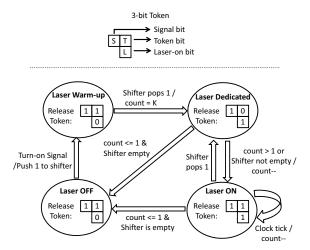

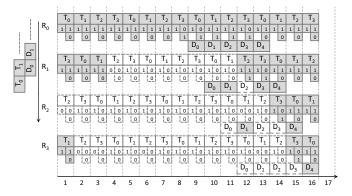

| FIGURE 19: | 3-bit Token and Laser Controller FSM                                                      |

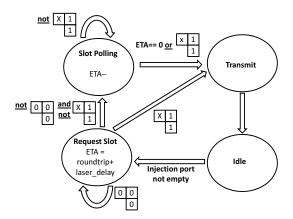

| FIGURE 20: | Writer Node FSM. 66                                                                       |

| FIGURE 21: | A Case Study: MWSR Laser Control Scheme=                                                  |

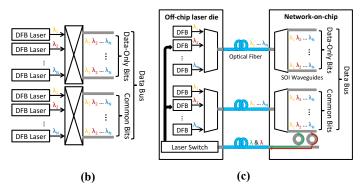

| FIGURE 22: | On-Chip and Off-Chip Laser Configurations                                                 |

| FIGURE 23: | Simulation flow chart                                                                     |

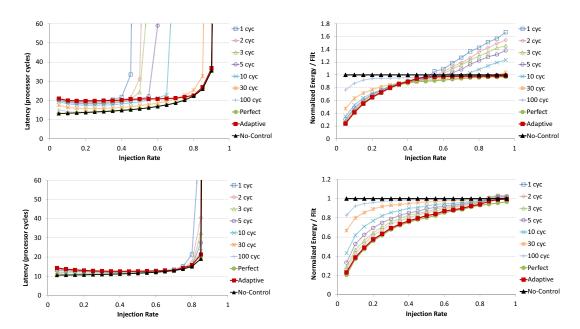

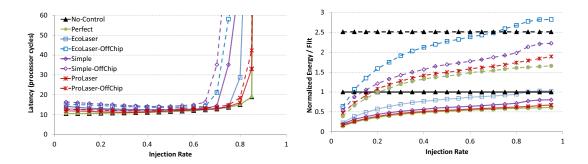

| FIGURE 24: | Load-Latency and Energy per Flit for radix-16 MWSR( top row ) and SWMR ( bottom           |

|            | row ) Crossbars                                                                           |

| FIGURE 25: | MWSR Scalability Analysis                                                                 |

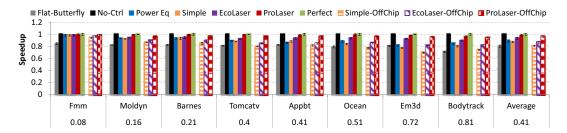

| FIGURE 26: | Speedup for radix-16 (top) and radix-64 (bottom) MWSR on a hypothetical multicore         |

|            | without thermal constraints                                                               |

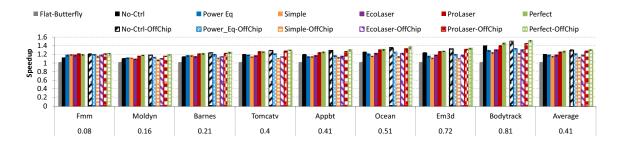

| FIGURE 27: | Speedup over CMesh for radix-16 (top) and radix-64 (bottom) MWSR crossbars under          |

|            | realistic thermal constraints                                                             |

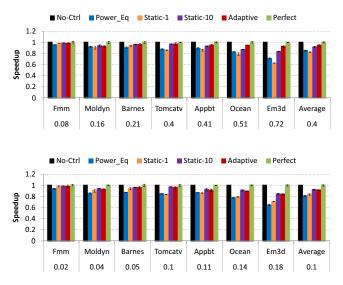

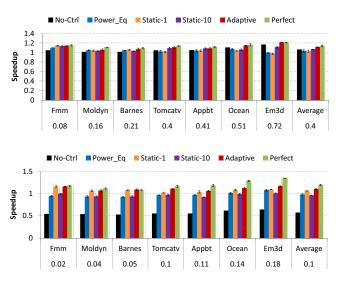

| FIGURE 28: | 8: Energy x Delay Product in radix-16 (top) and radix-64 (bottom) MWSR crossbar. The     |            |  |

|------------|------------------------------------------------------------------------------------------|------------|--|

|            | evaluated designs are from left to right: No-Ctrl (N), Power_Eq (E), Static-1 (1)        | ), Static- |  |

|            | 10 (10), Adaptive (A), and Perfect (P).                                                  | 82         |  |

| FIGURE 29: | Load-Latency (left) and Energy-per-Flit (right) for a radix-16 SWMR crossbar.            | 84         |  |

| FIGURE 30: | Speedup for radix-16 SWMR on a hypothetical multicore without thermal                    |            |  |

|            | constraints.                                                                             | 86         |  |

| FIGURE 31: | Speedup over Flat-Butterfly for radix-16 SWMR crossbar under realistic therma            | al         |  |

|            | constraints.                                                                             | 88         |  |

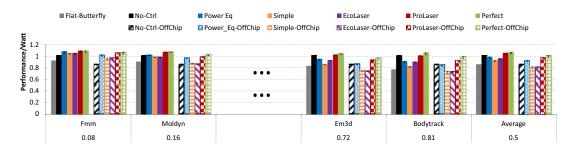

| FIGURE 32: | Performance per Watt over No-Ctrl for radix-16 SWMR crossbar under realistic             | thermal    |  |

|            | constraints.                                                                             | 89         |  |

| FIGURE 33: | Energy Per Instruction for radix-16 SWMR crossbar. The evaluated designs are             | from left  |  |

|            | to right:Flat-B., No-Ctrl, Power_Eq (Eq), Simple, EcoLaser (Eco), ProLaser (Proceedings) | ro), and   |  |

|            | Perfect and their Off-chip implementations (-Off)                                        | 89         |  |

| FIGURE 34: | Speedup over Flat-Butterfly for Firefly topology under realistic thermal                 |            |  |

|            | constraints                                                                              | 90         |  |

| FIGURE 35: | Performance per Watt over No-Ctrl for Firefly topology under realistic thermal           |            |  |

|            | constraints.                                                                             | 91         |  |

| FIGURE 36: | Energy Per Instruction for Firefly topology. The evaluated designs are from left         | to right:  |  |

|            | Flat-B., No-Ctrl, Power_Eq (Eq), Simple, EcoLaser (Eco), ProLaser (Pro), and             | Perfect    |  |

|            | and their Off-chip implementations (-Off).                                               | 91         |  |

| FIGURE 37: | Laser Turn-on Latency Tolerance.                                                         | 92         |  |

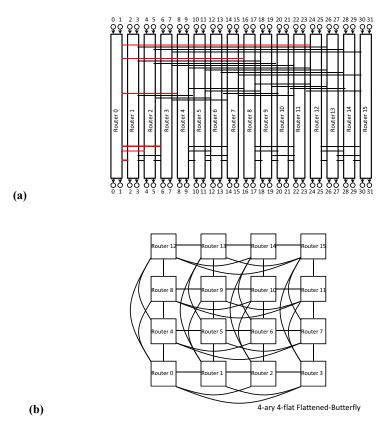

| FIGURE 38: | Electrical link (a) and Serpentine waveguide (b) layout for flattened butterfly to       | pology96   |  |

| FIGURE 39: | On-chip (a) and Multi-chip (b) Divergent Flattened Butterfly Layout                       |

|------------|-------------------------------------------------------------------------------------------|

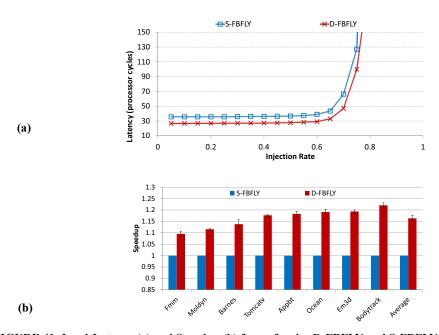

| FIGURE 40: | Load-Latency (a) and Speedup (b) for on-chip D-FBFLY and S-FBFLY layouts102               |

| FIGURE 41: | Load-Latency (a) and Speedup (b) for wafer size D-FBFLY and S-FBFLY layouts102            |

| FIGURE 42: | Flattened Butterfly Configurations                                                        |

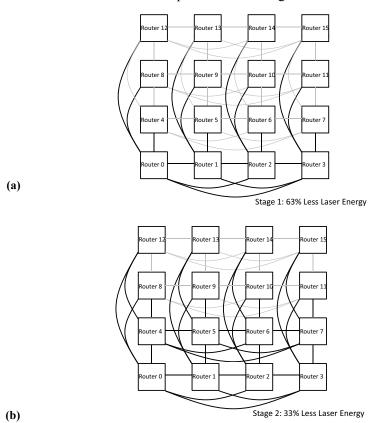

| FIGURE 43: | Laser-gating stages for the Flattened Butterfly Network                                   |

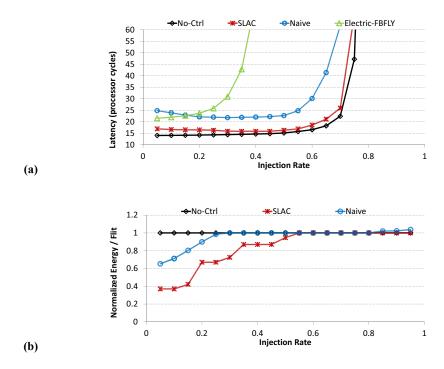

| FIGURE 44: | Load-Latency (a) and Laser Energy per Flit (b) for Flattened Butterfly topology with No-  |

|            | Ctrl, SLAC, Naive Control                                                                 |

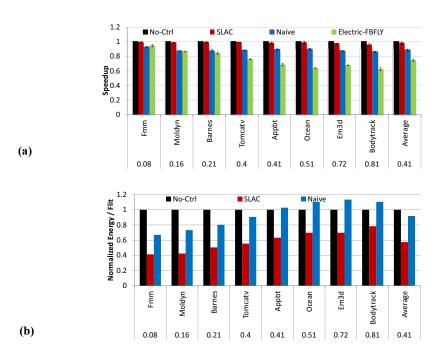

| FIGURE 45: | Speedup (a) and Laser Energy per Flit (b) for a multicore with No-Ctrl, SLAC, Naive       |

|            | Control and Electric-FBFLY                                                                |

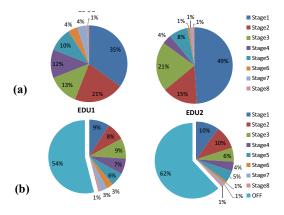

| FIGURE 46: | Fraction of time spent in each Stage                                                      |

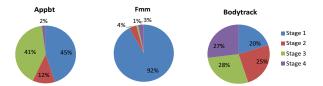

| FIGURE 47: | Speedup (a) and Laser Energy per Flit (b) for a Multi-chip with No-Ctrl, SLAC and         |

|            | Naive Control                                                                             |

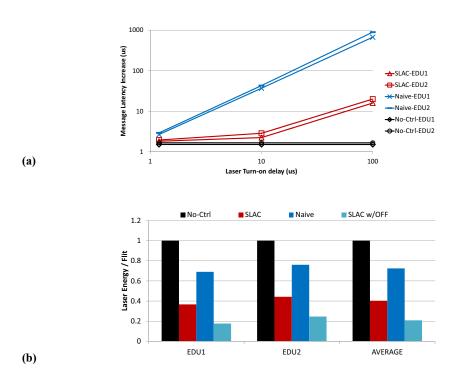

| FIGURE 48: | Message Latency(a) and Laser Energy per Flit (b) for a Datacenter Networks with No-       |

|            | Ctrl, SLAC, Naive Control                                                                 |

| FIGURE 49: | Fraction of time spent in each Stage                                                      |

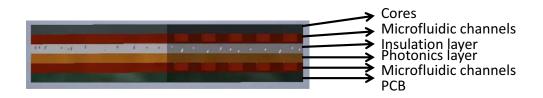

| FIGURE 50: | Proposed Parka Architecture                                                               |

| FIGURE 51: | Simulation flow chart                                                                     |

| FIGURE 52: | Transient analysis of temperature fluctuations in the photonics die                       |

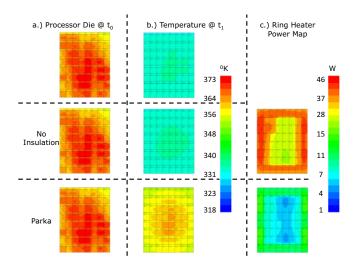

| FIGURE 53: | Case study: Impact of thermal insulation on the photonics layer temperature and the ring- |

|            | heating power consumption                                                                 |

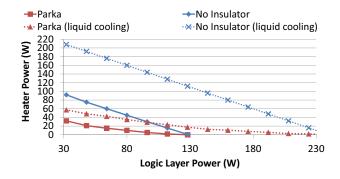

| FIGURE 54: | Ring -Heating Power vs. Processor Die Power                                               |

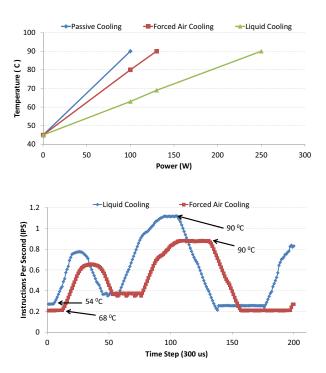

| FIGURE 55: | a.)Processor die temperature vs. processor power consumption, b.) Temperature trace  |

|------------|--------------------------------------------------------------------------------------|

|            | (running appbt) of a multicore                                                       |

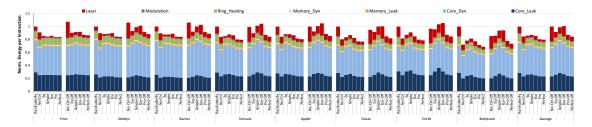

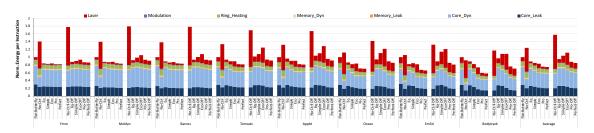

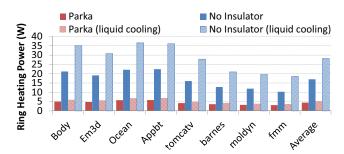

| FIGURE 56: | Average ring-heating power consumption while running real world applications 130     |

| FIGURE 57: | Parka's impact on the processor die temperature                                      |

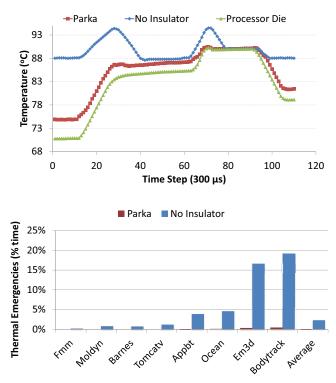

| FIGURE 58: | Temperature trace (appbt) presenting thermal emergencies in a multicore, and the     |

|            | percentage of execution time spent under thermal emergencies                         |

| FIGURE 59: | Realistic Multicore Performance with Parka                                           |

| FIGURE 60: | Liquid cooling solutions                                                             |

| FIGURE 61: | Liquid cooling solution with PARKA                                                   |

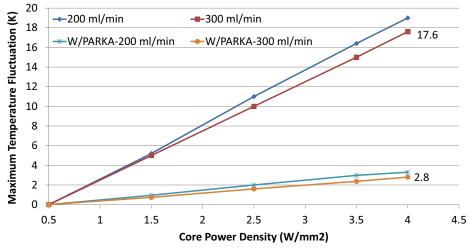

| FIGURE 62: | Maximum temperature fluctuation at the photonics layes with the microfluidic cooling |

|            | solution, with and without an insulation layer                                       |

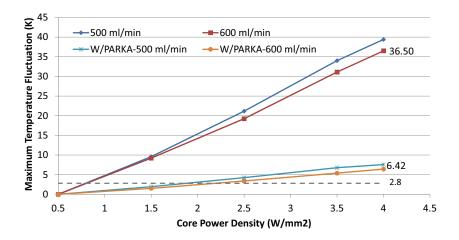

| FIGURE 63: | Maximum temperature fluctuation at the photonics layes with the microfluidic cooling |

|            | solution, with and without an insulation layer.                                      |

## List of Tables

| Table     | Title                                   | Page |

|-----------|-----------------------------------------|------|

| TABLE 1.  | Nanophotonic Parameters for Galaxy      | 34   |

| TABLE 2.  | Architectural Parameters.               | 36   |

| TABLE 3.  | Scalability of Galaxy.                  | 39   |

| TABLE 4.  | Architectural Parameters.               | 75   |

| TABLE 5.  | Nanophotonic Parameters and Laser Power | 76   |

| TABLE 6.  | Architectural Parameters.               | 98   |

| TABLE 7.  | Nanophotonic Parameters and Laser Power | 100  |

| TABLE 8.  | Architectural Parameters.               | 108  |

| TABLE 9.  | Nanophotonic Parameters and Laser Power | 109  |

| TABLE 10. | Architectural Parameters.               | 122  |

| TABLE 11. | Workload Details                        | 123  |

| TABLE 12. | Nanophotonic Parameters.                | 124  |

### Chapter 1

### Introduction

Providing high bandwidth density and low latency communication over long distances, with low signal modulation cost nanophotonic interconnects promise to meet performance needs of the scaled-out single-chip multiprocessors and multi-chip designs. Multi-chip designs can leverage nanophotonic interconnects to realize high performance "virtual chips" with the aggregate area and performance much higher than the single-chip multiprocessors. Previous research has focused on designing photonic network topologies, that provide high performance while keeping the power consumption low. However, due to physical limitations of photonic devices and laser sources, the laser power and ring heating power remain the most significant sources of power consumption in photonic interconnects. Schemes that lowers the laser power and ring-heating power consumption improves the energy-efficiency of the photonic interconnects, which makes them even more attractive solution for high performance single-chip and multi-chip processors.

Multi-chip designs can reach scales impossible to realize with conventional single-chip architectures (Macrochip integration). However, to deliver commensurate performance, multi-chip architectures require a cross-chip interconnect with bandwidth, latency, and energy consumption well beyond the reach of electrical signaling. On top of that, the performance and the scalability of the single-chip designs are highly limited due to increased power density and limited off-chip pin counts, whereas multi-chip designs breaks free of these limitations. Motivated by these facts, we propose Galaxy, an architecture that enables

the construction of a many-core "virtual chip" by connecting multiple smaller chiplets through optical fibers. The low optical loss of fibers allows the flexible placement of chiplets, and offers simpler packaging, power, and heat requirements. At the same time, the low latency and high bandwidth density of optical signaling maintain the tight coupling of cores, allowing the virtual chip to match the performance of a single chip that is not subject to area, power, and bandwidth limitations. We evaluate the performance, power, energy, and thermal profile of Galaxy, and compare it against single-chip designs (*processor disintegration*) and multi-chip designs (*macrochip integration*). Galaxy is up to 3.4x faster (1.8-2.2x on average) over single-chip alternatives with electrical, photonic, or hybrid interconnects, achieves up to 6.8x smaller energy-delay product (2.6x on average), and scales to 4K cores while being 2.5x faster at 6x lower laser power than a waveguide-based design.

The high-speed and low-cost modulation of light make photonic interconnects an attractive solution for manycore processors' communication demands. However, high optical loss of many nanophotonic components results in high power requirements for the laser source and thermal sensitivity of photonic devices force designers to have power hungry chip level ring-heating solutions. As a result, the laser power and the ring heating power consumption remains a potential issue that needs to be addressed.

In order to address the high laser power consumption problem, we propose a laser control scheme EcoLaser, which opportunistically turns the laser off during periods of low activity to save energy, and leaves it on during periods of high activity in order to meet the high bandwidth demand. EcoLaser capitalizes on recent advancements in Ge lasers [42,47], which enable energy-efficient on-chip laser sources that can be turned on or off within nanoseconds. We propose a collection of static and dynamic laser control mechanisms and policies that approximate the maximum possible savings, and we present detailed designs of EcoLaser for both SWMR and MWSR optical crossbars. We evaluate the impact of EcoLaser on the

performance and energy of a multicore, and our results indicate that EcoLaser saves between 24-77% of the laser power for radix-16 and radix-64 SWMR and MWSR crossbars real-world workloads.

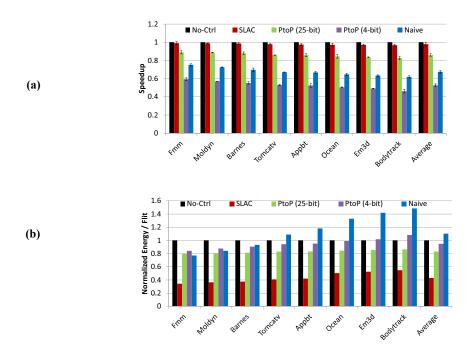

Improving upon EcoLaser, we propose ProLaser, which is a laser control scheme that achieves higher laser energy savings for all utilization levels while minimizing the additional laser turn-on delay overhead of the laser control, by keeping the majority of the data-bus inactive while sending small (dataless) messages, and anticipating upcoming messages to turn the lasers on ahead of time. We evaluated the impact of ProLaser on the performance and energy of a multicore running a range of synthetic and scientific workloads under realistic physical constraints, and show that it saves between 49-88% of the laser power, it outperforms the current state of the art by 2x on average, and closely tracks (within 2-6%) a perfect prediction scheme with full knowledge of future interconnect requests. On top of that, the power savings of ProLaser allow for providing a higher power budget to the cores, which enables them to run faster. Employing ProLaser on a topology with SWMR crossbars (Firefly [57]) allows the multicore to achieve 1.5-1.7x speedup (1.6x on average) and attain 35-52% lower energy consumption per instruction (40% on average).

Energy proportionality is desirable for not only the on-chip photonic interconnects, but also the multi-chip systems and the datacenters with photonic networks. Such scaled-out systems exploit scalable photonic network topologies such as "flattened butterfly" topology. Flattened butterfly topology provides path-diversity between source and destination pairs, so it can provide high throughput while keeping the hardware cost at bay. Laser power-gating is a promising technique to mitigate high laser power consumption of the photonic interconnects, however, it reduces the performance when messages have to wait for the laser turn-on. We propose SLAC, a laser control scheme for flattened butterfly network which turns off majority of the network to save laser energy, while maintaining a fully connected network which removes the laser turn-on latency from the critical path and causes minimal (next to nothing) performance decrease.

SLAC turns off majority of the network when the utilization is low to save energy and activates additional stages when the utilization is high to provide better performance. From an on-chip interconnect to a datacenter network, any network with flattened butterfly topology can take advantage of SLAC. Our results show that, for on-chip and multi-chip applications, SLAC can save up to 67% laser energy while reducing the performance by only 2% while running real-world workloads. On a flattened butterfly datacenter network, SLAC saves 79% laser energy on average while running traces collected from university servers.

Ring heating power consumption remains a potential issue that needs to be addressed. The nanophotonic devices are highly susceptible to temperature-induced changes, because their refraction index changes rapidly with temperature. In a multicore processor there is a potential for significant variation in temperature, so micro-ring resonators must be stabilized at a higher temperature using ring heaters which may consume significant amount of energy. As current silicon-photonic designs are predominantly based on microring resonators which are highly temperature-sensitive devices, these thermal fluctuations in turn throw the microring resonators off-resonance and prevent the optical interconnect from functioning. To keep the microrings resonating at their appropriate wavelengths, the designers employ trimming, which is a technique that dynamically shifts the microring's resonant wavelength towards the red through heating, or shifts it towards the blue through current injection. However, trimming by current injection causes instability and thermal runaways [51], thus microrings are typically maintained at a constant temperature using the heaters only. The microrings are tuned to a temperature slightly over the maximum temperature that the microprocessor reaches, because only the heaters are employed. Unfortunately, this means that the heaters need to work continuously to keep the microrings at such high temperature, and at the same time the majority of the heating power is wasted as it dissipates through the package to the heat sink. As a result, it is common for microring heaters to consume upwards of 40W [51], mostly of which is wasted. To make matters worse, this thermal energy heats up the logic layer to temperatures very close to its operational limit, which

forces the system to throttle the cores, thereby reducing the performance. The runaway heat also increases the frequency and magnitude of the thermal emergencies, and accelerates the aging of the logic die.

The solution we propose is rather simple: thermally decouple the 3D-stacked logic die from the photonics die by introducing an insulating layer between them to maintain higher thermal stability and easier trimming. We propose "Parka", a nanophotonic NoC that encases the photonic die in a thermal insulator that keeps its temperature stable with low energy expenditure, while minimizing the spatial and temporal thermal coupling between logic and silicon-photonic components. Our results indicate that Parka reduces the ring heating power by 3.8x on average across our workload suite. Moreover, the energy savings allow for providing a higher power budget to the cores, which enables them to run faster. Parka on a radix-16 crossbar allows the multicore to achieve 11-23% speedup (34% max) over a baseline scheme with no insulation, depending on the cooling solution used.

The rest of the document is organized as follows. In Chapter 2, we present the Galaxy Architecture and evaluate its performance and energy characteristics. In Chapter 3, we introduce EcoLaser and ProLaser, we present the SLAC laser control for Flattened Butterfly network in Chapter 4, and we evaluate their energy savings and performance characteristics. We present PARKA, which improves thermal stability of the photonic devices by introducing a 3D architecture with an insulator layer, in Chapter 5. We discuss the future work in Chapter 6, comment on related research in and conclude in Chapter 7.

### Chapter 2

### **Energy-Efficient Disintegrated Processor Design**

Advanced silicon fabrication allows for exponentially increasing transistor counts, which allows for increasingly dense multicore chips. However, physical limitations in area, yield, off-chip bandwidth, and power limit the scalability of single chip designs. Area and yield considerations push for small die sizes, and the latest ITRS models reflect the competitive requirements for afford ability by targeting flat chip-size trends for both high-performance and cost-performance processors (lowered to 260 mm² and 140 mm² respectively [23]). At the same time, while transistor counts grow exponentially, voltage scaling has slowed. This has lead to a dramatic increase in power density with decreasing feature size [31], creating chips that require a power budget beyond what is practical today to operate and leading to "dark silicon" [22,26,49]. Moreover, the limited pin count and low efficiency in off-chip communication severely limit the off-chip bandwidth [61], rendering it increasingly difficult to feed all cores with data fast enough to keep them busy. This bandwidth wall hampers the scalability of future CMPs and their performance, even for highly-parallel workloads [26].

As a result, multicore scalability is being rapidly pushed to an end. Physical constraints limit single chip designs to either a relatively small number of cores, beyond which scaling becomes impractical, or to designs that trade single-core performance for high aggregate instruction throughput, which can only be achieved if all cores are simultaneously employed by the executing workload. For example, a single core in Intel i7-3960X has a peak theoretical performance of 187 *GFLOPS*, but only 6 such cores fit in the chip's area and power budget. In contrast, Intel Phi 5110P features 60 cores, but at only 17 *GFLOPS* per core, and NVIDIA GTX-680 features 1536 CUDA cores but at a paltry 2 *GFLOPS* each.

Alternative designs can break free of some physical limitations, but not all. Aggregating together several discrete smaller dies instead of having a large one (*disintegration*) overcomes the area and yield limitations [13], as only few dies need to be replaced if they are faulty [5,13]. At the same time the total silicon area of the aggregate chip can scale beyond reticle size limits, allowing the aggregate chip to reach scales impossible to realize with a monolithic design (*macrochip integration*). 3D-die stacking can realize these benefits by vertically connecting several smaller dies in a package with through-silicon-vias (TSVs). However, 3D-die stacking incurs significant challenges in power delivery and heat removal, and is best employed when the additional dies implement low-power applications (e.g., DRAM). By contrast, high-power applications (e.g., high-performance processors), are ideally spread out as an array of chips, allowing for power delivery to and heat removal from each individual die directly. Unfortunately, connecting a large array of chips at high bandwidth presents unique challenges.

Limitations in the density of chip I/O and package routes dramatically constrain the number of links that can be routed across chips, and severely constrain bandwidth. A 580 mm<sup>2</sup> die can have 25600 pins to the package substrate at a pitch of 150  $\mu$ m, but the substrate-to-board pitch is 0.8 mm which allows only 3844 pins to the board from a 5 cm x 5 cm package [23]. This forces the use of over-clocked and high power serial links for chip-to-chip communication. Thus, using electrical links (SerDes) [60] on an FR-4 board incurs significant energy consumption or long delays (20 pJ/bit typically, and at best 2.5 pJ/bit and 2.5 ns latency over 4 inches of electrical strip [60]) as the designers have to trade energy for performance or viseversa. Silicon interposers (i.e., 2.5D integration) allow chips to connect laterally within the same package through "bridge" silicon chips, thus exploiting the high density of die-to-package and on-chip wires. However, this enables only modest-sized arrays of chips, and their scalability is further limited by the low speed of on-chip wires, especially over distances longer than 10 mm [39,41].

With the introduction of nanophotonics, systems can break free of all these limitations. The low latency and high bandwidth density of optical signaling can facilitate efficient off-chip communication and bring physically distant chips effectively close together. This makes it possible to build a physically large but logically dense many-core "virtual chip" by optically connecting several chiplets together [13,39,54].

To integrate chiplets into a larger system, NSiP [13] uses silicon-nitride waveguides across chiplets within a package, and the Oracle Macrochip [39] uses silicon waveguides etched on a wafer. While these proposals mitigate the area, yield, and memory bandwidth limitations of conventional designs, they do not address the power constraints. The high optical loss of silicon waveguides (typically 0.1-0.3 dB/cm [8]) makes routing long cross-chiplet optical channels impractical from a power standpoint. Thereby, designs utilizing waveguides are confined to a small physical space (e.g., a wafer [39] or a package [13]). This increases the thermal density to the point where liquid cooling is required to avoid thermal runaways [39,41], or confines the aggregate "virtual chip" to power limitations not much different from a monolithic design [13]. Aggressive technology can produce low-loss waveguides (0.05 dB/cm [41]) which enable the wide separation of discrete chiplets. However, these waveguides are 20x wider than conventional ones. Their high area occupancy forces the use of exceedingly narrow chiplet-to-chiplet links (e.g., 2-bit links for an 8x8 chiplet array [39,41]) which in turn imposes significant serialization that degrades performance. Thus, to design a large "virtual chip" using waveguides, one either has to suffer high optical loss which multiplies the power requirements, or employ narrow paths which impose serialization, hurt performance, and in turn increase energy consumption.

In contrast, Galaxy is designed to push back the power constraints, in addition to overcoming the area, yield, and bandwidth limitations, while matching the high performance of unconstrained tightly-coupled chips. Optical fibers have tremendously low optical loss that is measured in kilometers (0.2 dB/km), so very long channels can be drawn at very low power. Galaxy uses fibers for cross-chiplet communication, and

also guarantees that each optical path employs only a small fixed number of couplers, keeping the optical loss and the corresponding laser power low. These two design choices allow spreading discrete chiplets far apart in physical space to minimize heat transfer and lower the power density of the virtual chip, which in turn enables each chiplet to operate at a higher frequency than power-limited designs. At the same time, the propagation speed of light in fibers  $(0.676 \ c)$  is considerably higher than in silicon waveguides  $(0.286 \ c)$ , or electrical lines on FR-4 boards  $(0.5 \ c)$ , allowing for low-latency communication over long distances. Compared to electrical lines, fibers transmit at about 33x lower energy per bit [4].

Previous research [39] dismissed the use of optical fibers for cross-chiplet communication under the assumption that chips connect to fibers at a relatively large 250  $\mu m$  core pitch, not the 20  $\mu m$  pitch of optical proximity couplers that silicon waveguides use. Hence, the chip-to-chip bandwidth over fibers would not improve much over area solder balls connected to package routes. Galaxy overcomes this consideration by exploiting new tapered coupler technologies that couple an array of fibers at 250  $\mu m$  pitch into an array of waveguides at 20  $\mu m$  pitch at the edge of the chip [44]. Our results indicate that fibers can provide sufficient bandwidth for communication to chiplets and to memory, allowing for much wider data paths than low-loss but slow silicon waveguides, and in turn boost both the performance and the energy efficiency of the multi-chip system by several times.

In summary, optical fibers are faster, impose lower optical loss, and require lower energy than available alternatives for chiplet communication. They are also flexible, allowing for arbitrary placement of chiplets (e.g., across boards within a rack) without the need for additional coupling. Thus, fibers are especially suitable for long, inter-chiplet optical channels, as they are easy to route, and can even go off the plane or off the board. Galaxy utilizes optical fibers for cross-chiplet communication and offers simple packaging, power, and heat requirements, yet provides the performance advantages of a tightly-coupled system. While prior works have touched upon some of these issues in the context of multi-chip architectures [4, 5, 13, 39,

41, 54], to the best of our knowledge, this is the first work that quantifies the impact of disintegration and multi-chip integration on power constraints, and provides an analysis of the performance, power, energy, and thermal characteristics of several multi-chip architecture alternatives.

It is important to note that Galaxy is just one design that supports processor disintegration and macrochip integration. Other topologies and designs are possible. Our goal is not to perform a full design-space sweep and advocate Galaxy as the optimal solution. Rather, we aim to demonstrate that macrochip integration and processor disintegration can match the performance of designs that are not limited by power and off-chip bandwidth, effectively breaking free from the limitations of today's chips. More specifically, our contributions are:

- We quantify the performance and energy impact of power and bandwidth constraints in monolithic single-chip designs, and the limitations of electrical links and SOI waveguides when used for chip communication.

- We propose Galaxy, an architecture that allows both processor disintegration and macrochip integration. Galaxy builds a many-core "virtual chip" by connecting multiple smaller chiplets through optical fibers.

- 3. We evaluate the performance, power, energy, and thermal characteristics of Galaxy, and compare it against single-chip designs (processor disintegration) and multi-chip designs (macrochip integration). Galaxy is up to 3.4x faster (1.8-2.2x on average) over single-chip alternatives with electrical, photonic, or hybrid interconnects, achieves up to 6.8x smaller energy-delay product (2.6x on average), and scales to 4K cores while being 2.5x faster at 6x lower laser power than a waveguide-based design.

#### 2.1 .The Galaxy Architecture

Galaxy builds a physically-large but logically-dense many-core "virtual chip" by optically connecting many discrete chiplets together. Each chiplet consists of a logic die with cores, caches, and support circuits, and a die with photonic devices and waveguides. The two dies are stacked in 3D: electrical signals from the logic die travel via TSVs to the photonic die, where they are converted to optical signals, and vise-versa. Galaxy utilizes electrical signaling for nearest-neighbor communication within a chiplet, and silicon waveguides for long-distance communication within a chiplet. Silicon waveguides are compatible with CMOS processes [11] and they are more efficient for long-distance on-chip communication than electrical signaling [57], leaving global on-chip wires redundant. The on-chip photonic interconnect extends across chiplets by coupling light to an optical fiber at the edge of the chip [44]. A photonic link in Galaxy consists of an off-chip laser source, optical fibers, fiber to on-chip waveguide couplers, SOI waveguides on the chip, a laser splitter, ring modulators, drop filters, and Germanium-based photodetectors.

#### 2.1.1 Network Topology

Galaxy employs a hybrid electrical/photonic interconnect. It extends Firefly [57] to support cross-chiplet communication at low power by minimizing coupler crossings and the number of sharers of each optical path. Figure 1(a), depicts a 5-chiplet Galaxy design. The colored squares within each chiplet represent routers. The routers within a chiplet are divided into local clusters. Each cluster contains exactly one router per remote chiplet. In our example, there are 4 clusters per chiplet, with 4 routers per cluster. A local cluster in Chiplet 3 consists of neighboring black, orange, blue, and green routers (red outline in Chiplet 3, Figure 1(a)). Each cluster supports a number of cores based on a concentration factor. The cores and routers in a cluster are electrically connected. In our example, we use concentration 1 and an electrical ring

FIGURE 1: (a) Galaxy layout, (b) MWSR optical crossbar, and (c) router architecture.

within the cluster (other topologies are possible). A source-destination pair within the same cluster uses only electrical links.

Clusters communicate with each other through optical crossbars. Every optical crossbar is represented by coloring routers with the same color. For example, the pink routers in Chiplet 0 and the pink routers in Chiplet 1 belong to the same optical crossbar. Each optical crossbar extends across two chiplets. In our example, the crossbar between Chiplet 0 and Chiplet 1 consists of the pink routers in Chiplets 0 and 1, the U-shaped waveguides that connect these routers within each chiplet, and the fibers that connect the two chiplets. Figure 1(b) shows a close-up of that crossbar, where the pink routers have been re-colored to assist a detailed explanation later in the section.

Routing a packet from Chiplet 0 to Chiplet 1 is carried by traversing the corresponding optical crossbar. This is done in 3 steps: (1) Route electrically within the source cluster in Chiplet 0 to a pink router; (2) Take the optical link and arrive at the pink router of the destination cluster in Chiplet 1; (3) Route electrically within the destination cluster to the final destination. Communication between any two clusters is performed similarly. Source-destination clusters within the same chiplet use only the silicon waveguides in that chiplet. If the clusters are at different chiplets, the packet will traverse the waveguides within the source chiplet, the fiber connecting the two chiplets, and the waveguides in the destination chiplet.

In Galaxy, every cluster has as many routers as remote chiplets, and every router in a cluster is connected to a different optical crossbar. Thus Galaxy forms a point-to-point network between chiplets. Also, every crossbar extends across all clusters of the two chiplets it connects. Thus, each cluster has a direct connection to every cluster of every chiplet. A packet that traverses an optical link will directly reach a router in the destination cluster which is very close to the final destination, and every packet traverses the optical link only once. This minimizes coupler crossings and optical loss: every optical path is short because it extends across only two chiplets, and has at most 3 couplers (including the laser coupling).

In general, if each chiplet has X clusters, each with Y routers, and a concentration of c, the proposed Galaxy architecture can connect (Y+1) chiplets, using radix-(2X) optical crossbars, supporting a total of c\*Y\*X\*(Y+1) cores. The example in Figure 1 is a case with X=Y=4, c=1, for a total of 80 cores.

Firefly [57] uses Single Writer Multiple Reader (SWMR) optical crossbars, which use global broadcast channels to send messages or to reserve a channel, thereby increasing power consumption. Galaxy adopts a modified Firefly topology with Multiple Writer Single Reader (MWSR) optical crossbars. In MWSR crossbars, each router "listens" on a dedicated channel and sends flits on the listening channels of all the other routers in the crossbar. Figure 1(b) illustrates an MWSR crossbar that extends over chiplets 0 and 1, with 8 senders and 8 receivers. Every router is shown with a distinct color. Every router receives data from its own channel, which is shown with the same color as the receiver router, and writes 7 other channels which are the listening channels of the other routers in the crossbar. Galaxy adopts FairQuota [56] to guarantee that only a single router transmits on a channel at any moment, avoid starvation, and provide QoS support.

Figure 1(c) shows a hybrid electrical/optical router in Galaxy. Routers store the flits received from the electrical or optical networks in electrical buffers, after optical to electrical (O/E) conversion if needed. Two electrical input and output ports route packets on the electrical local cluster ring. The third electrical input

and output port is used for data injection. Each router has a pair of dedicated optical receiving channels, the upstream and downstream channels. The dark blue and green routers in Figure 1(b) send messages to the purple router through its upstream channel, while the rest send messages to the purple router through its downstream channel. Thus, 2 extra ports are added on the input side of the router to receive packets from the dedicated optical receiving channels from both directions. On the output side, 7 additional output ports switch outgoing packets to different optical channels.

#### 2.1.2 Switch Arbitration and Flow Control

The electrical switch within each router is arbitrated using conventional electrical arbiters, and uses conventional credit-based flow control. The optical crossbars require arbitration of the optical channels and the buffers at the optical receiving ports. The optical channel arbitration is equivalent to a global switch allocation, and is achieved using a 1-pass optical token stream [73] that extends across two chiplets.

Because the optical links are traversed at most once, at most two Virtual Channels (VCs) are needed for the optical channels. The buffers of each optical VC channel are arbitrated using a separate optical VC token stream. Every router keeps a count of the available buffer space for each VC, and distributes an optical VC token every cycle as long as there is available space. A sender acquires a VC token of its intended VC before entering the arbitration for the data channel. An acquired VC token is held even if the sender fails the subsequent channel arbitration. To keep the balance of VC tokens, the tokens perform a double traversal. The receiver router of a channel first sends the VC tokens in the direction opposite to the data channel (back-traversal), all the way to the origin of the laser injection point, skipping all the senders on the way. Then, the VC token goes through O/E and E/O conversion, and is re-modulated onto a VC token stream in the same direction as the data channel (forward-traversal). The unused VC tokens eventually arrive back at the receiver and are re-collected to ensure that the receiver always knows how many VC

FIGURE 2: Latency, Energy / bit, and Energy x Delay product for electrical links, SOI waveguides, and fibers.

tokens are consumed by the senders. The extra OE/EO conversion at the origin of the data channel ensures that only short optical waveguides are used.

#### 2.1.3 Inter-Chiplet Optical Connection

Galaxy employs optical fibers to connect chiplets, rather than silicon waveguides. Compared to electrical links, fibers offer lower latency, and two orders of magnitude lower energy/bit and energy-delay-product across the entire range of possible chiplet-to-chiplet distances (Figure 2). Similarly, fibers are almost 2x faster than SOI waveguides, and achieve between 2-10x lower energy/bit and energy-delay-product (Figure 2), mainly due to the high relative optical loss of typical silicon waveguides. Extremely low-loss waveguides (0.05 *dB/cm* [41]) reduce the difference in optical loss from 15000x [8,9] to 2500x, but they are much wider (20x) than conventional waveguides. This forces the design of narrow data-paths (e.g., 2-bit chiplet-to-chiplet links for an 8x8 chiplet array [39,41]) which impose serialization and degrade performance. Silicon interposers underperform waveguides (and by extension fibers) for inter-chiplet communication [41], and in addition confine designs to a single package, which in turn increases thermal density and allows only small-scale systems. Thus, fibers are especially suitable for long, inter-chiplet channels. Our findings in Figure 2 corroborate prior research [41].

Fibers connect to chiplets through a coupler that tapers an array of fibers at  $250 \,\mu m$  pitch down to  $20 \,\mu m$  pitch channels, and couples them into an array of SOI waveguides at the edge of the chip [44]. The mea-

sured coupling loss caused by the refraction index change from fibers to the waveguides including misalignment is 0.8 dB, and the internal loss of the coupler caused by tapering the channels is 3 dB. Misalignment within  $0.7 \mu m$ ,  $0.4 \mu m$ , and  $0.7 \mu m$  in the lateral, vertical, and optical axes produces losses under 1 dB [44]. The performance of the tapered coupler is comparable to that of an optical proximity coupler (3.5 dB coupler loss, plus 0.5 dB per  $1 \mu m$  misalignment in the y-axis, plus less than 1 dB loss due to misalignment within  $2.5 \mu m$  in the x- and z-axis [80]).

#### 2.1.4 Nanophotonic Parameters and Power Budget

On-chip lasers dissipate a lot of power and heat up the chip, thus Galaxy adopts off-chip WDM-compatible lasers. The laser is brought on chip via optical fibers connected to tapered couplers [44], and a splitter distributes it to low-loss on-chip waveguides [8]. Tapered couplers [44] also transfer the laser from on-chip waveguides to the off-chip optical fibers and vise-versa. Galaxy uses the modulators, demodulators, drop filters, splitters, and detectors introduced in [2]. The modulation and demodulation energy is  $150 \, fJ/bit$  at  $10 \, GHz$  [2]. The optical parameters assumed in Galaxy are detailed in Table 1.

The example configuration of Galaxy which we evaluate in this paper consists of 10 radix-8 MWSR cross-bars that transfer 64-bit flits. We assume a modest 16-way DWDM, thus Galaxy uses a total of 320 fibers (128 fibers attached to each chiplet) and 40960 ring resonators (8192 per chiplet). Because every optical channel requires a 1-token-pass arbitration mechanism, a total of 20 additional fibers and 3840 rings are used for arbitration. Another 80 rings and 10 fibers are used for forward clock signal distribution [41].

To calculate the total ring heating power we extend the method by Nitta *et al*. [51] by incorporating the heat generated by the cores. The cores heat up the photonic layer, and the ring heaters provide the remaining heat necessary to bring the photonic layer within the ring tuning range. As current injection may cause a

TABLE 1. Nanophotonic Parameters for Galaxy

|                             | per Unit         | Total          |

|-----------------------------|------------------|----------------|

| Splitters                   | 0.2 <i>dB</i>    | 0.2 <i>dB</i>  |

| Waveguide Loss              | 0.3 <i>dB/cm</i> | 1.5 <i>dB</i>  |

| Fiber Loss                  | 0.2 <i>dB/Km</i> | ~0 dB          |

| Nonlinearity                | 1 <i>dB</i>      | 1 <i>dB</i>    |

| Coupler Loss                | 3.8 <i>dB</i>    | 7.6 <i>dB</i>  |

| Modulator Insertion         | 0.5 dB           | 0.5 dB         |

| Ring Through                | 0.01 <i>dB</i>   | 1.28 <i>dB</i> |

| Filter Drop                 | 1.5 <i>dB</i>    | 1.5 <i>dB</i>  |

| Photodetector               | 0.1 <i>dB</i>    | 0.1 <i>dB</i>  |

| Total Loss                  |                  | 13.68 dB       |

| <b>Detector Sensitivity</b> |                  | -20 dBm        |

| Laser Power per Wavelength  |                  | 0.233 mW       |

| <b>Total Laser Power</b>    |                  | 1.195 W        |

thermal runaway [51], we only consider trimming by heating. Section 2.2.2 details the model. While Galaxy may benefit from trimming power saving methods [51], they are out of the scope of this paper.

Figure 3 demonstrates the sensitivity of Galaxy's laser power to the nanophotonic parameters. The laser power is sensitive to the coupler loss, but relatively insensitive to the other parameters, indicating that our results will likely hold under a wide range of nanophotonic device technologies.

When evaluating electrical links for off-chip communication, existing literature typically omits inefficiencies in the generation and delivery of the electrical power. By analogy, and to ease comparisons with prior work, we didn't include the generation and delivery cost in the laser power calculations presented in the remainder of this paper. For completeness, however, here we calculate the laser power including all these overheads. The additional coupling loss increases the laser power to 2.9W. Assuming 10% efficiency for the WDM-compatible off-chip laser [82], the wall-socket laser power is 29W.

### 2.2 .Experimental Methodology

We evaluate the performance of an example 5-chiplet 80-core Galaxy on a full-system cycle-accurate simulation infrastructure using Flexus 4.0 [27,75] integrated with Booksim 2.0 [15] and DRAMSim 2.0 [62]. Table 2 details the architectural modeling parameters. We target a 16nm technology, and have updated our tool chain accordingly based on ITRS projections [23]. We follow the SimFlex sampling methodology [75] with 95% confidence intervals. We model performance as the number of user instructions committed per unit of time [75]. The simulated system executes a selection of SPLASH benchmarks and scientific workloads.

We compare Galaxy against three single-chip CMPs, all of which implement the architecture described in Table 2. The first CMP uses an all-electrical 2D-Concentrated Mesh on-chip interconnect with express links [15] and concentration of 4 (CMeshExp). Concentrated mesh is often chosen for on-chip networks as it maps well to a 2D-VLSI planar layout with low complexity. We evaluated a regular 2D-Mesh and a 2D Concentrated Mesh without express links, and found that CMeshExp outperforms the other designs on all metrics (performance, power, and energy). Thus, we only show results for CMeshExp. We model routers with 8 input and output ports and a 3-cycle routing delay. Routers are connected through 166-bit bi-directional links with a 1-cycle link delay.

FIGURE 3: Laser power sensitivity to optical parameters.

**TABLE 2. Architectural Parameters.**

| CMP Size              | 80-cores, 580 mm <sup>2</sup>                                                                                                                                        |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processing<br>Cores   | ULTRASPARC III ISA, max 5 <i>GHz</i> , OoO, 8-stage pipeline, 4-wide dispatch/retirement, 96-entry ROB                                                               |

| L1 Cache              | split I/D, 64 <i>KB</i> 2-way, 2-cycle load-to-use, 2 ports, 64-byte blocks, 32 MSHRs, 16-entry victim cache                                                         |

| L2 Cache              | shared, 512 <i>KB</i> per core, 16-way, 64-byte blocks, 14-cycle hit, 32 MSHRs, 16-entry victim cache                                                                |

| Memory<br>Controllers | One per 4 cores, or 4 MCs per chip. 1 channel/MC Round-robin page interleaving;                                                                                      |

| Main Memory           | DDR3, 80 <i>GB</i> , 8 <i>KB</i> pages, 20 <i>ns</i> access latency Interfaces: (a) Conventional pins, (b) Optically-connected memory (OCM) [2], (c) 3D-stacked [39] |

| Networks              | CMesh, Corona, Firefly, Galaxy, Oracle Macrochip                                                                                                                     |

The second CMP uses an all-optical MWSR crossbar (Corona [74]), implemented with 256-bit data channels creating 80 MWSR crossbars. We model global switch arbitration using an optical token ring. A token for each node, which represents the right to modulate on the node's wavelength, continuously passes around all nodes on a dedicated arbitration waveguide. A node grabs and absorbs a token to transmit a packet, and then releases the token to allow other nodes to obtain it. We estimate 16cm long waveguides for the Corona chip, resulting in 8 cycles token round-trip time at 5 *GHz*. The third CMP implements a hybrid interconnect where clusters of electrically-connected cores are connected through an SWMR optical crossbar implemented entirely on chip (Firefly [57]).

We model Galaxy with 1-cycle latency for processing an optical token request [73]. Each Galaxy router can initiate a maximum of 8 token requests per cycle, but can utilize at most 2 acquired tokens [73]. Galaxy uses 1-pass token stream arbitration for combined VC and channel arbitration. We estimate that the round-trip time of a token is also 8 cycles. The input buffers are implemented as a DAMQ [70], with packets queued separately based on their destination. A data packet contains 512 bits, which are divided into eight 64-bit flits.

FIGURE 4: Simulation flow chart.

# 2.2.1 Power and Temperature Modeling

All systems we model employ Dynamic Voltage and Frequency Scaling (DVFS) to lower the voltage and frequency of a chip or chiplet when it reaches the limits of safe operational temperature (without loss of generality, we assume  $90^{\circ}C$ ). Figure 4 shows the flow diagram of our simulation tool chain. We collect runtime statistics from full-system simulations, and use them to calculate the power consumption of compute cores, caches, and memory controllers using McPAT [46], and the power consumption of the electrical and optical networks using DSENT [69] and the analytical model by Joshi *et al.* [33] respectively. Based on these power estimates, we calculate the temperature of the chip and chiplet assemblies using HotSpot 5.0 [67] and FloTherm [77], a computational fluid dynamics tool that models the heat transfer between chiplets through air flow and convection. The estimated temperature is then used to refine the leakage power estimate, and we iteratively calculate the power and temperature profiles until the system reaches a stable state. We use the stable-state power and temperature estimates to adjust DVFS, and repeat the process until we identify a DVFS setting for which the chip stays just below  $90^{\circ}C$ , or operates at the maximum 5 *GHz*.

# 2.2.2 Resonant Ring Heater Modeling

To calculate the total ring heating power for Galaxy, Corona, and Firefly, we extend the method by Nitta *et al.* [51] by additionally accounting for the heating of the photonic die by the operation of the cores. We model the thermal characteristics of a 3D-stacked architecture where the photonic die sits underneath the logic die using the 3D-chip extension of HotSpot [67]. For each target architecture (Corona, Firefly, and Galaxy) we measure the maximum temperature of the logic die during the execution of each one of the workloads. Then, we tune the micro-rings to the maximum of all the observed temperatures that the logic layer reaches across all benchmarks executing on the target architecture, plus a small margin. When a workload executes, we calculate the ring heating power required to maintain the entire photonic die at the micro-ring trimming temperature during the entire execution.

# 2.2.3 Modeling Memory and Physical Constrains

To demonstrate the ability of disintegrated architectures to break free of power and bandwidth limitations, we evaluate Galaxy against all possible single-chip CMP combinations: power-constrained, off-chip bandwidth-constrained, fully constrained (i.e., power and bandwidth), and unconstrained.

We evaluate power-constrained CMPs by employing DVFS to keep the chips within  $90^{\circ}C$ . To evaluate CMPs that are not subject to power constraints, we allow the chips to run at the maximum speed allowed by the design (5 GHz), by disregarding power and thermal limits. We evaluate bandwidth-constrained single-chip CMPs by assuming a conventional DDR3 memory, and limit the total memory bandwidth by utilizing ITRS [23] pin projections for a 5 cm x 5 cm package, assuming 1/3 of the pins are used for power, 1/3 are used for I/O, and the remaining 1/3 are used for memory. The memory pins are distributed equally among four memory controllers (MCs). To evaluate designs that are not limited by memory bandwidth, we increase the number of pins well beyond ITRS projections and commensurately increase the number of

TABLE 3. Scalability of Galaxy.

| # of<br>Cores | Multi-Chip<br>Architecture |                  | Bandwidth<br>per Chip<br>(TB/s) | Laser<br>Power<br>(W) | Serialization<br>Overhead<br>(cycles) | Link<br>Latency<br>(cycles) |

|---------------|----------------------------|------------------|---------------------------------|-----------------------|---------------------------------------|-----------------------------|

| 320           |                            | Fibers           | 10                              | 4.0                   | 1                                     | 2                           |

|               | Galaxy                     | Waveguides       | 5                               | 4.9                   | 2                                     | 10                          |

|               |                            | Electrical links | 0.320                           | 3.9                   | 32                                    | 12                          |

| 1088          |                            | Fibers           | 20                              | 27.0                  | 2                                     | 10                          |

|               |                            | Waveguides       | 5                               | 26.0                  | 8                                     | 20                          |

|               |                            | Electrical links | 0.640                           | 26.8                  | 64                                    | 12                          |

| 4160          |                            | Fibers           | 40                              | 47.6                  | 4                                     | 10                          |

|               |                            | Waveguides       | 10                              | 44.9                  | 16                                    | 20                          |

|               |                            | Electrical links | 0.320                           | 47.9                  | 512                                   | 12                          |

| 4096          | Oracle MacroChip           |                  | 0.630                           | ~40.0                 | 64                                    | 20                          |

MCs, until more pins or more MCs no longer increase performance. For our workloads, we reach this point when 5x more pins are distributed across 20 MCs. Fully constrained designs operate within the power, memory bandwidth, and thermal limits. Fully unconstrained designs operate beyond the power, thermal, and bandwidth limits and cannot realistically be built; however, they provide the highest performance that a particular architecture can achieve, limited only by the maximum speed allowed by the design (5 *GHz* in our evaluation). While we compare Galaxy to both constrained and unconstrained single-chip CMPs, Galaxy is always modeled to conform to realistic power, bandwidth, and temperature limits.

Emerging memory technologies such as optically-connected memory (OCM) [2] or 3D-stacked memory [39] are not pin-limited, and can remove the memory bandwidth bottleneck for all CMP designs. Thus, we separately evaluate the performance of Galaxy against single-chip CMPs with OCM and 3D-memory, where each CMP employs 20 MCs (additional MCs provide no benefit). We model a 10 ns access latency for OCM [2] and a 2 ns access latency for 3D-Memory [39].

### 2.2.4 Modeling Large-Scale Designs

Galaxy can scale up to 1088 cores with 17 chiplets (64 cores each with concentration 4), and 4160 cores with 65 chiplets. When increasing the number of chiplets, we decrease the width of chip-to-chip links to

FIGURE 5: Load latency under uniform random traffic.

keep the network power consumption and component count within reasonable levels, and we faithfully model the serialization delay due to narrower datapaths, and increased link latency due to longer links. We evaluate the scalability of Galaxy by comparing it against (a) Galaxy with SOI waveguides and optical proximity (OPC) couplers [80], (b) Galaxy with electrical links (SerDes), and (c) the Oracle Macrochip [39]. For fairness, we adjust the datapath width of Galaxy alternatives so they fit into similar power envelopes, and then calculate the latency overhead. The Oracle Macrochip model closely follows [39,80]. Table 3 details the characteristics of each design. To keep the simulations tractable, we estimate the performance of the scaled-out designs by imposing the latency overheads of each scaled-out system from Table 3 on an 80-core 5-chiplet model. As we impose the scaling overheads onto same-size designs in all cases (80 cores, 5 chiplets), the higher core count of Galaxy compared to the Oracle Macrochip does not affect the results.

### 2.3 .Experimental Results

### 2.3.1 Network Performance

Figure 5 analyzes the load-latency of CMeshExp, Corona, Firefly, and Galaxy. CMeshExp saturates quickly, which is indicative of its relatively low bandwidth. Corona saturates at a little less than 0.7 injection rate, while Firefly reaches an injection rate of almost 0.8 before saturating. Galaxy trails Firefly closely, and falls only slightly short in performance. This is expected because Galaxy is similar to a 2-level

Firefly that creates a single datapath between two clusters, while packets in Firefly can take several alternate routes and utilize more of the available bandwidth. Nonetheless, the small difference indicates that Galaxy is a competitive interconnect.

## 2.3.2 Comparison to Single-Chip Designs